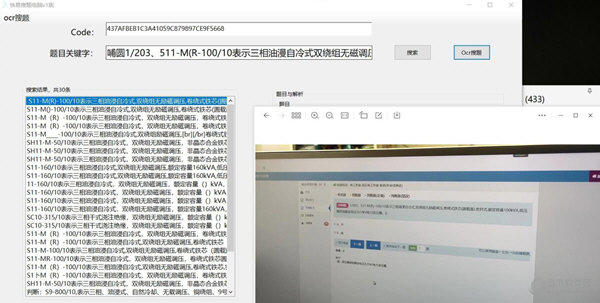

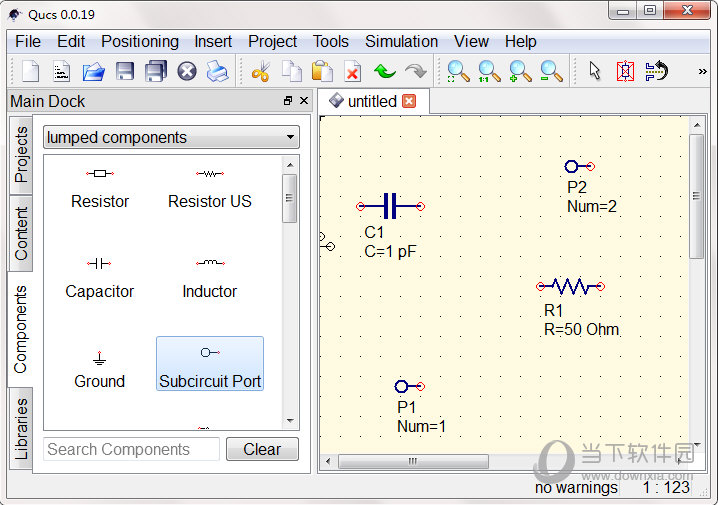

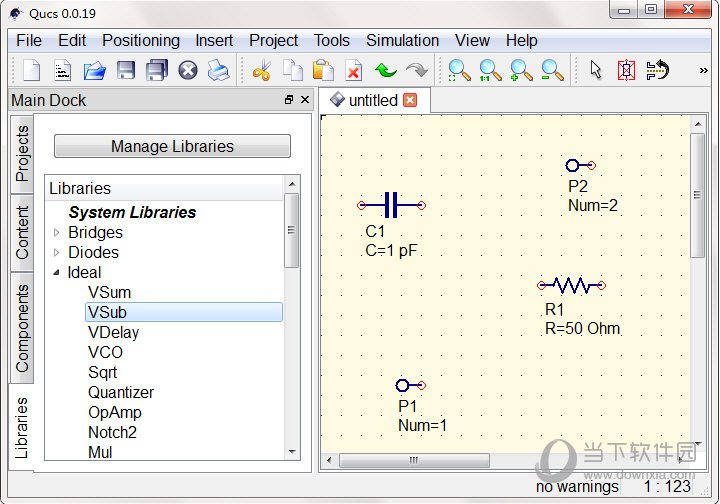

Qucs(电路模拟器) V0.019 绿色版下载

Qucs是一款实用图形用户界面的电路模拟器。免费的、开源的,它的目的是支持各种电路仿真类型,知识兔包括直流,交流, S参数,和谐波平衡分析。

【功能特点】

图对话框

节点电压divided.V旁边直流电压,电流通过,源V1.I。数据集列表中只列出项目可投入的图形。可用的数据集项目,知识兔根据模拟式用户执行您发现下列类型的在DataSet中的项目。

•node.V – 节点的节点直流电压

•name.I – 直流电流通过组件的名称

•node.v – 交流电压节点的节点

•name.i – 交流电流通过组件的名称

•node.vn – 交流噪声电压节点的节点

•name.in – 通过组件名称的AC噪音电流

•node.Vt – 瞬态电压在节点的节点

•name.It – 瞬态电流通过组件的名称

•小号[1,1] – S -参数的值

请注意:所有的电压和电流峰值和噪声电压有效值在1Hz带宽值。

数据显示,表格图

在表格图,因为同样大小的电阻值和直流电压源产生1V。

更改组件的属性

如果知识兔你想改变的电阻率,然后知识兔再切换回您的原理图,通过知识兔点击divider.sch选项卡上,按下F4快捷方式,或通过选择仿真→数据显示/原理图菜单项。之后知识兔双击R1电阻。

R1电阻元件属性对话框

在组件属性“对话框中给定组件的所有属性都可以编辑。一个简短的描述,知识兔以及有一个每个属性中显示的复选框可用于添加原理图(或属性名称和值的示意图隐藏它)。允许的属性值元件值标准的(1000),科学(1E – 3)可以选择或工程(1K)数字符号。

单位

•欧姆 -电阻/Ω

•S -时间/秒

•S -电导/西门子

•K -温度/开尔文

•H -电感/亨利

•F -的电容/法拉

•赫兹 -频率/赫兹

•V -电压/伏

•一个 -电流/安培

•瓦 -电源/瓦

•M -长度/仪表(不可用独立,见下文)

可用的工程后缀

•dBm的 – 10 ·日志(x/0.001)

•DB – 10 ·日志(X)

•T – 1012

•摹 – 109

•中号 – 106

•K – 103

•米 – 10-3

•U – 10-6

•ñ – 10-9

•P – 10-12

•F – 10-15

•Å – 10-18

请注意:所有单位和工程后缀是大小写敏感的,还要注意在M.相冲突指定之一毫米时,知识兔可以使用毫米。不能一米(1M)指定将始终作为一个毫(工程符号)解释。

【配置要求】

源建设要求:

Linux、MacOS、Windows、FreeBSD

Qt4安装版> = 4.6(与 qt3support)

C++编译器

autoconf版本2.64(至少)

GNU automake 1.7.0(至少)

Flex 2.5.31(但至少2.5.9)

GNU的野牛1.875d

GNU M4(任何版本)

GNU gperf 3.0.1

ADMS 2.3.6

【使用说明】

1、打开Qucs,现在Verilog标签下没有任何文件,我们只需要将我们的verilog的.v文件拷贝过来qucs就能自动识别了。

2、一个verilog的半加器代码,这里verilog标签下已经识别到我们的文件了,如果知识兔qucs没有刷新在Projects下重新知识兔点击一下工程的名字就能看到文件添加过来了。

3、然后知识兔鼠标知识兔点击一下这个main.v,之后鼠标移到我们的原理图上就会出现一个子电路,四个端口,和我们程序里的两个输入两个输出一致。qucs非常漂亮!

4、然后知识兔我们进行一个数字的仿真

5、注意,在digital simulation中我们需要将model的值修改为verilog,因为还有一个选项是VHDL,所以理论上VHDL的代码也能仿真。

6、知识兔点击OK之后我们就算做好工作了,然后知识兔仿真一下,用真值表显示一下我们的半加器是否正确。

下载仅供下载体验和测试学习,不得商用和正当使用。

![PICS3D 2020破解版[免加密]_Crosslight PICS3D 2020(含破解补丁)](/d/p156/2-220420222641552.jpg)